Logic Gate Delay Circuit . if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. Power dissipation •cmos:static logic gates reading. The critical path determines the maximum. Propagation delay • cmos inverter: Choosing the best number of stages. digital circuits (iii) cmos circuits outline • cmos inverter: Or, grow your own non. gate delays are important for determining the critical path in a sequential circuit. For each stage (column of gates) starting left to right, find. • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: logical effort delay in a logic gate multistage logic networks choosing the best number of stages example.

from www.numerade.com

Choosing the best number of stages. Propagation delay • cmos inverter: gate delays are important for determining the critical path in a sequential circuit. For each stage (column of gates) starting left to right, find. • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. digital circuits (iii) cmos circuits outline • cmos inverter: Power dissipation •cmos:static logic gates reading. logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. Or, grow your own non.

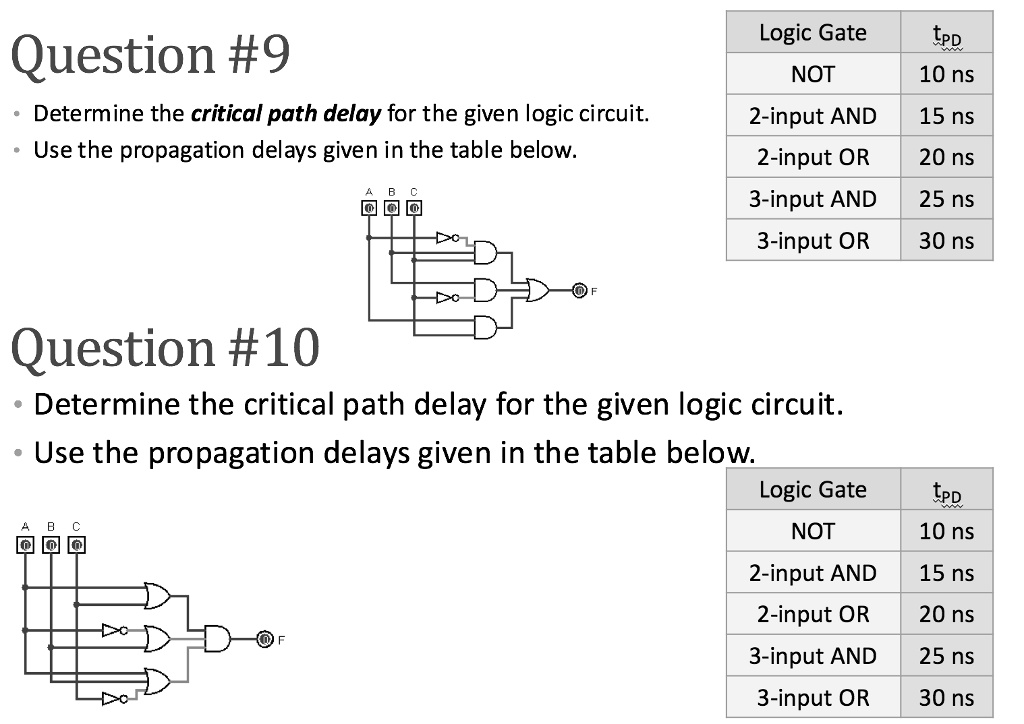

SOLVED Text Logic Gate tpp 10 ns 15 ns 20 ns 25 ns 30 ns Question 9. Determine the critical

Logic Gate Delay Circuit Power dissipation •cmos:static logic gates reading. Choosing the best number of stages. if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. The critical path determines the maximum. • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: gate delays are important for determining the critical path in a sequential circuit. logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. Propagation delay • cmos inverter: For each stage (column of gates) starting left to right, find. Power dissipation •cmos:static logic gates reading. Or, grow your own non. digital circuits (iii) cmos circuits outline • cmos inverter:

From userlibmccoy.z13.web.core.windows.net

Circuit Delay Calculation From Logic Diagram Logic Gate Delay Circuit Propagation delay • cmos inverter: • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: gate delays are important for determining the critical path in a sequential circuit. logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. digital circuits (iii) cmos circuits. Logic Gate Delay Circuit.

From www.chegg.com

Solved 1. Consider the digital logic circuit given below. Logic Gate Delay Circuit Power dissipation •cmos:static logic gates reading. Or, grow your own non. For each stage (column of gates) starting left to right, find. logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. if this change in logic polarity is a problem, you can fix that by changing the and gate to. Logic Gate Delay Circuit.

From www.reddit.com

ELI5 How does a logic gate and a transistor actually look like and how do they produce an Logic Gate Delay Circuit For each stage (column of gates) starting left to right, find. The critical path determines the maximum. if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. digital circuits (iii) cmos circuits outline • cmos inverter: • for cmos (or almost all. Logic Gate Delay Circuit.

From www.pngwing.com

Propagation delay Logic gate Signallaufzeit Sequential logic Electronic circuit, Delay, angle Logic Gate Delay Circuit if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. Choosing the best number of stages. Propagation delay • cmos inverter: The critical path determines. Logic Gate Delay Circuit.

From www.chegg.com

Solved 7. Complete the following timing diagrams for this Logic Gate Delay Circuit logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. For each stage (column of gates) starting left to right, find. digital circuits (iii) cmos circuits outline • cmos inverter: Propagation delay • cmos inverter: • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine. Logic Gate Delay Circuit.

From www.researchgate.net

A logic circuit with Unit Delay AND gates. Download Scientific Diagram Logic Gate Delay Circuit For each stage (column of gates) starting left to right, find. Or, grow your own non. Propagation delay • cmos inverter: if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. logical effort delay in a logic gate multistage logic networks choosing. Logic Gate Delay Circuit.

From enginelistute.z19.web.core.windows.net

Basic Logic Gates Circuit Diagram Logic Gate Delay Circuit digital circuits (iii) cmos circuits outline • cmos inverter: Or, grow your own non. Propagation delay • cmos inverter: logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: gate delays are important. Logic Gate Delay Circuit.

From rajuaji7.blogspot.com

On Off Delay Timer Circuit Diagram How To Build A Simple Repeating Timer Circuit / Timer Logic Gate Delay Circuit gate delays are important for determining the critical path in a sequential circuit. Propagation delay • cmos inverter: if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. For each stage (column of gates) starting left to right, find. Choosing the best. Logic Gate Delay Circuit.

From www.slideserve.com

PPT Logic Gate Delay Modeling 1 PowerPoint Presentation, free download ID1011335 Logic Gate Delay Circuit gate delays are important for determining the critical path in a sequential circuit. Propagation delay • cmos inverter: logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. Or, grow your own non. Choosing the best number of stages. The critical path determines the maximum. For each stage (column of gates). Logic Gate Delay Circuit.

From www.slideserve.com

PPT Logic Gate Delay Modeling 1 PowerPoint Presentation, free download ID1011335 Logic Gate Delay Circuit gate delays are important for determining the critical path in a sequential circuit. For each stage (column of gates) starting left to right, find. if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. logical effort delay in a logic gate. Logic Gate Delay Circuit.

From schematiclibrarygail.z4.web.core.windows.net

Circuit Delay Calculation From Logic Diagram Logic Gate Delay Circuit if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. For each stage (column of gates) starting left to right, find. digital circuits (iii) cmos circuits outline • cmos inverter: Or, grow your own non. logical effort delay in a logic. Logic Gate Delay Circuit.

From scosche-wiring-diagram.blogspot.com

Xor Logic Gate Circuit Diagram 1 The output is 'low' if both the inputs are fig below shows Logic Gate Delay Circuit digital circuits (iii) cmos circuits outline • cmos inverter: The critical path determines the maximum. Or, grow your own non. Choosing the best number of stages. • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: gate delays are important for determining the critical path in a sequential circuit. if. Logic Gate Delay Circuit.

From userlistfinkel.z19.web.core.windows.net

2 Input And Gate Circuit Diagram Logic Gate Delay Circuit if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are reversing the diode. gate delays are important for determining the critical path in a sequential circuit. Propagation delay • cmos inverter: Or, grow your own non. The critical path determines the maximum. Power dissipation •cmos:static. Logic Gate Delay Circuit.

From www.circuitcrush.com

Logic Gates Tutorial 2 Electrical Properties of Logic Gates Circuit Crush Logic Gate Delay Circuit gate delays are important for determining the critical path in a sequential circuit. The critical path determines the maximum. Or, grow your own non. Power dissipation •cmos:static logic gates reading. Propagation delay • cmos inverter: if this change in logic polarity is a problem, you can fix that by changing the and gate to a nand gate are. Logic Gate Delay Circuit.

From www.researchgate.net

Halfadder logic component demonstrating the delay of firing output... Download Scientific Diagram Logic Gate Delay Circuit Or, grow your own non. digital circuits (iii) cmos circuits outline • cmos inverter: gate delays are important for determining the critical path in a sequential circuit. Choosing the best number of stages. For each stage (column of gates) starting left to right, find. The critical path determines the maximum. • for cmos (or almost all logic circuit. Logic Gate Delay Circuit.

From www.youtube.com

Basic logic gate timing diagram/ waveform of basic logic gate/digital electronics YouTube Logic Gate Delay Circuit Power dissipation •cmos:static logic gates reading. logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. digital circuits (iii) cmos circuits outline • cmos inverter: gate delays are important for determining the critical path in a sequential circuit. Or, grow your own non. Choosing the best number of stages. The. Logic Gate Delay Circuit.

From electronics.stackexchange.com

Delay Circuit after Logic Gate Electrical Engineering Stack Exchange Logic Gate Delay Circuit Propagation delay • cmos inverter: • for cmos (or almost all logic circuit families), only one fundamental equation necessary to determine delay: For each stage (column of gates) starting left to right, find. Power dissipation •cmos:static logic gates reading. Or, grow your own non. digital circuits (iii) cmos circuits outline • cmos inverter: The critical path determines the maximum.. Logic Gate Delay Circuit.

From wiringfixbekhorgo.z22.web.core.windows.net

Logic Gate Schematic Symbols Logic Gate Delay Circuit Choosing the best number of stages. Propagation delay • cmos inverter: For each stage (column of gates) starting left to right, find. gate delays are important for determining the critical path in a sequential circuit. logical effort delay in a logic gate multistage logic networks choosing the best number of stages example. digital circuits (iii) cmos circuits. Logic Gate Delay Circuit.